Perhaps most people think that Nvidia, Qualcomm, and Mobileye have won the architectural battle for advanced autopilot. Does this mean that traditional car chip companies have surrendered? Just the opposite. They still seem to be planning new angles to maintain their position or even defeat their opponents. Where will NXP's new real-time car processor be in this upheaval?

NXP last week unveiled two new families of real-time processors to meet OEM's different needs for next-generation automotive architecture.

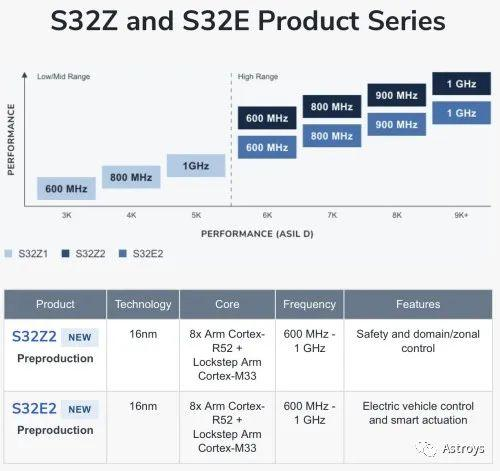

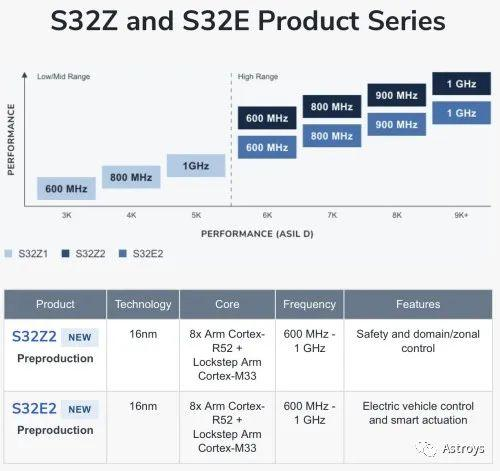

Both chips belong to the NXP S32 automotive platform, S32Z is responsible for safety processing and domain/zonal control, while S32E is responsible for electric vehicle control and intelligent drive.

NXP uses a variety of popular terms to describe new products: software-defined vehicles, zonal/domain controllers, end-to-end secure communications, secure multi-ECU integration, and so on. This is a term that automakers like to use, and NXP is catering to their needs.

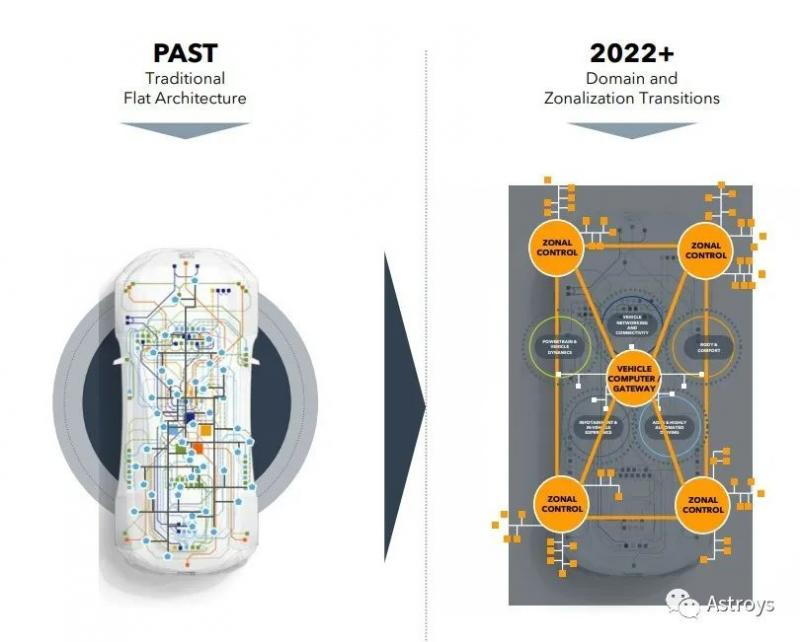

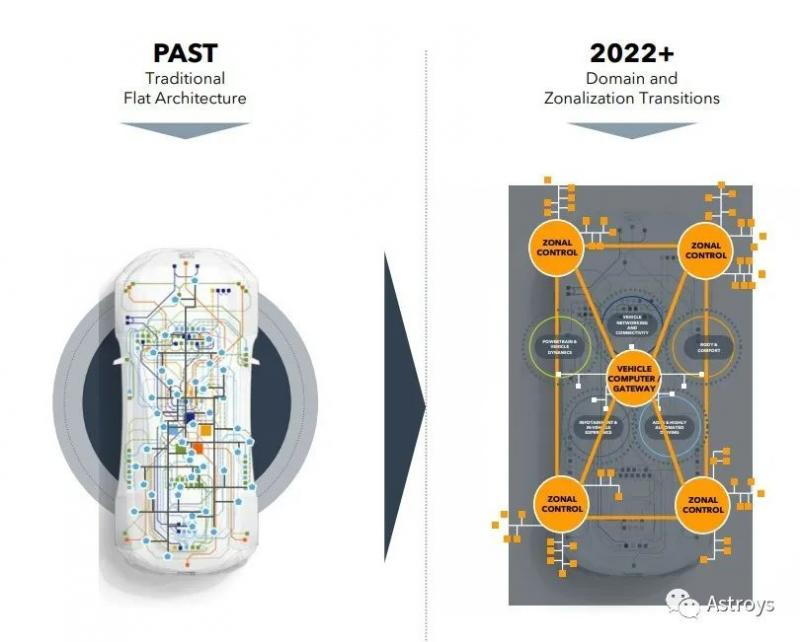

If we look at NXP's new product launch in a broader context, we can see some important changes in the auto market.

First, the architecture of the next generation of cars is still changing. Second, chip suppliers are divided into two camps, those with large-scale high-computing GPU/CPU and those without. Third, the battle for car platforms is more about software than hardware. The big question is whether anyone has really gained an advantage by integrating all the software on the next-generation car platform.

NXP obviously wants to play this game. But can it really do this without a large central brain based on CPU/GPU?

Polarization of chip pattern

Today, the market is clearly polarized, with players with AI/ML capabilities (Nvidia, Qualcomm, Intel/Mobileye) driving the central brain in the next generation of vehicles, while traditional companies that do not have this capability (NXP, Infineon, Renesas, TI) belong to another camp. NXP, on the other hand, positions himself as the leader of the non-central brain camp.

Once upon a time, automakers thought the $100 CPU was unacceptable. In the past few years, however, leading OEM has begun to embrace this central brain trend.

Despite the problem with Tesla, automakers want a platform that allows them to keep adding ADAS features, even if they don't plan to develop fully autopilot.

Perhaps companies like NXP and Infineon have been thinking that automakers will wake up and give up expensive GPU/CPU solutions and go back to them (traditional car chips).

But the leading OEM has developed its own software on this platform after being familiar with Nvidia's solution. They didn't look back, which caught NXP, Infineon, TI or Renesas by surprise.

NXP seems to have another set of plans to position its S32G or S32Z as a matching chip "next to those brains." NXP chips can act as security processors or for redundant decision-making and execution. NXP's S32G or S32Z can even offload some functions from large central chips, reducing the pressure on central computing.

NXP already has many products in its S32G product line, including S32G (gateway) and S32R (radar). Now there are S32E (vehicle drive and battery management) and S32Z (domain/zonal control). All the designs are designed to meet the needs of vehicles, of course, there is no central brain here. Although NXP announced a partnership with Kalray about a year and a half ago to launch the Bluebox 3.0 solution (designed for safe automotive high-performance computing), NXP has not yet released a roadmap for its AV/ADAS processor.

Domain vs. Zonal

It is true that the auto industry wants to merge former independent ECU into fewer ECU. However, Brain Carlson, head of product and solutions marketing at NXP, says different automakers have different schedules and paths. Some companies adopt the domain architecture directly, while others start with zonal.

"Domain is about integrating logic software," says Carlson. This is like putting the foundation into general-purpose software and focusing on OTA. The focus of the Zonal is to simplify wiring (you can lose almost 80 kilograms). "

Carlson says some automakers may soon enter zonal. Other companies may be a hybrid architecture of domain and zonal. NXP wants to cater to the needs of OEM, no matter what architecture they develop.

As Carilson explains, real-time applications are distributed throughout the vehicle. The advantage of the S32Z and S32E, he said, is that they "can be deployed in multiple locations of the vehicle."

Towards 5nm

NXP had an ambitious plan to push its automotive processors into the 5nm process. This shocked many people, as most of the car MCU is still on the traditional node.

The plan seems to be progressing steadily as planned. In a keynote speech at Computex 2022 last month, NXP's CEO Kurt Sievers demonstrated a TSMC 5nm-based "test chip" that conforms to the ASIL D standard. But the S32E and S32Z that have just been released are still 16nm. When will the 5nm chip be released?

Carlson explained: "We are already working on the design and production of 5nm chips. What we show is what we really have, on which we can actually run functional applications. Not everything, of course. " The software of 5nm chip is not ready yet and is still being perfected step by step.

There is no exact statement as to which S32 processor will start using 5nm MagneNXP.

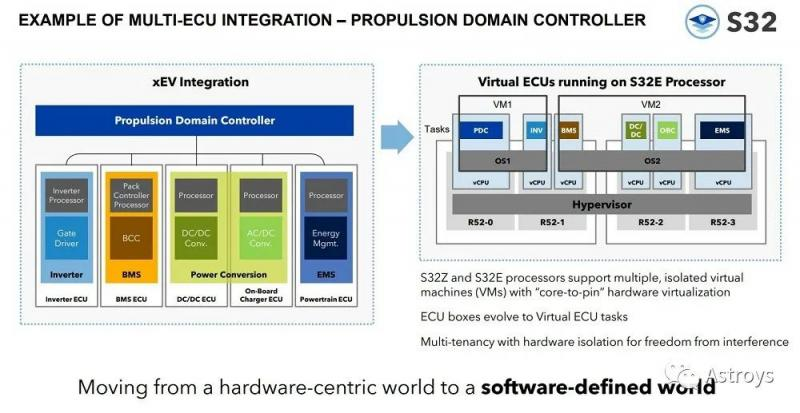

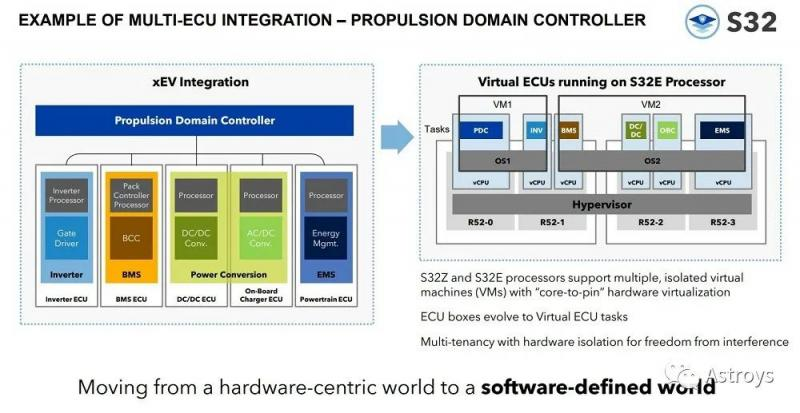

Hardware isolation of Core-to-pin

The most prominent feature of S32E and S32Z is the hard isolation of "core-to-pin" as described by NXP. According to NXP, this approach is critical for automakers that want to combine different ECU functions (currently implemented in separate ECU boxes) on a new processor.

Carlson explained that from the processor to the pins of the chip, Imax O, task, functions and controls can be fully virtualized in hardware.

Other chip companies offer virtualization, software hypervisor or hardware-assisted hypervisor. "We provide complete chip virtualization," Carlson stressed. "they are isolated from each other and look like the previous boxes."

Both S32Z and S32E have the hardware virtualization capability of "processor core-to-pin", allowing "multiple real-time applications to be developed and run on the device at the same time".

According to Carlson, this hardware virtualization allocates associated memory, peripherals, memory bandwidth, and device (Imax O) pins to the processor task.There are no other processor tasks to interfere with. Tasks appear as separate, isolated functions as if they were in a separate ECU.

This is a big problem for OEM, which wants to integrate multiple Tier 1 applications on the same chip. On S32Z or S32E devices, different applications from these Tier 1 will not affect the operation of other applications.

At the Embedded World event last week, NXP showed running eight different tasks, injecting errors into one of them, but not the others.

Plans for the future

After Qualcomm's failed attempt to buy NXP, NXP seemed unprepared and had no partners in the burgeoning battle for central computing. This is because NXP may have been counting on Qualcomm to share AI and ML capabilities.

Although fully self-driving vehicles have not yet been mass-produced, people in the industry have begun to think that Nvidia, Qualcomm and Intel/Mobileye have won the AV/ADAS market. Of course, there are different views that there is still a long way to go before the winner appears.

NXP believes that the continued iteration of the next generation of automotive architecture is a positive sign.

As OEM strives to reduce the number of ECU, a solution is needed so that software from different vendors (Tier 1, integration partners) runs well on the same device. Here, NXP sees an opportunity to promote core-to-pin.

"OEM wants software developed by all parties to run on the same device," Carlson said. But what would you do? Can you coordinate them to work together? It is not hard to imagine that these apps will kill each other for resources. "

But through the hard isolation of core-to-pin, NXP hopes to provide a means of peaceful coexistence.

Candice ·

Candice ·